Question: Multi - cycle synchronous neuron datapath core m x q unsigned integer multiplier with synchronous output: Synapses will be modeled by combinational m x q

Multicycle synchronous neuron datapath core

m x q unsigned integer multiplier with synchronous output: Synapses will be modeled by

combinational m x q unsigned integer multipliers with each xi input of size m bits and each weight of

size q bits. You will implement a register with update control in addition to clk control at the output

of the multiplier such that a computed output will only be available on the rising edge of the clk if

update signal is ON If update is OFF, the register will retain its previous value.

Code:

module MxQMultiMQP;

input:M;

input:Q;

output:P:

output control;

wire:XYS;

wire carryout;

assign Y bM&QM&Q;

assign X M&QM&QM&Q;

nbitRCA MbYXScarryout;

defparam Mn ;

assign P carryoutSM&Q;

endmodule

input nbit adder: Generate an adder unit that can add four nbit numbers as part of the neuron

function y You will need to figure out how many bits you need to allow for the output for any n

Code:

module nbitRCA carryinXYScarryout;

parameter n;

input carryin;

input n:XY;

outputn:S;

output carryout;

wire n:C;

genvar i;

assign C carryin;

assign carryout Cn;

generate

fori; in; ii

begin: fulladderRCA

fulladder M CiXiYiSiCi;

end

endgenerate

endmodule

Unsigned division by n: Generate a combinational divider function that divides an unsigned mbit

input integer by a power of n to generate a smaller unsigned integer. This is the second operation

in the neuron function y How many bits is the smaller unsigned integer at the output?

Code:

module divbyn #parameter m parameter nMQ;

input m:M;

output mn:Q;

assign Q M n;

endmodule

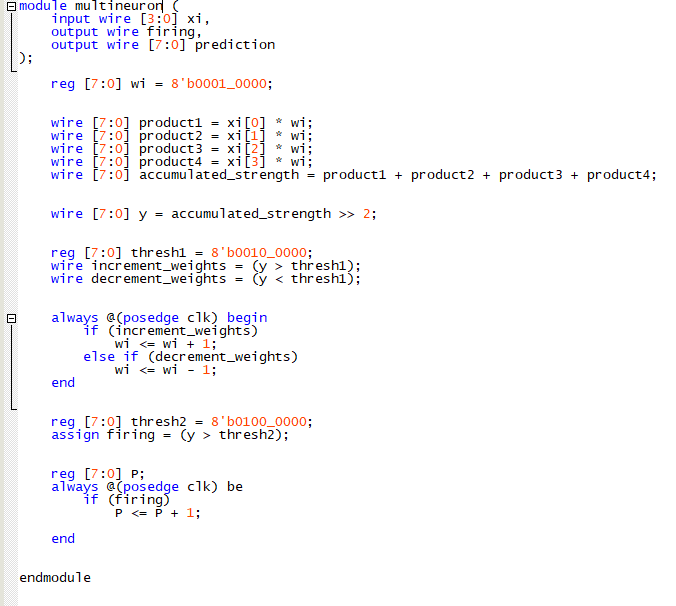

Develop a Verilog HDL testbench to do cornercase verification of consecutive input xi patterns to

verify the basic functionality of datapath core eg weight and Prediction counters counting in the

right direction. Achieving a firing event.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock