Question: Multi-Cycle Arch. Given the following code. Assume that x and y are arrays of words and the base address of x is stored in R1

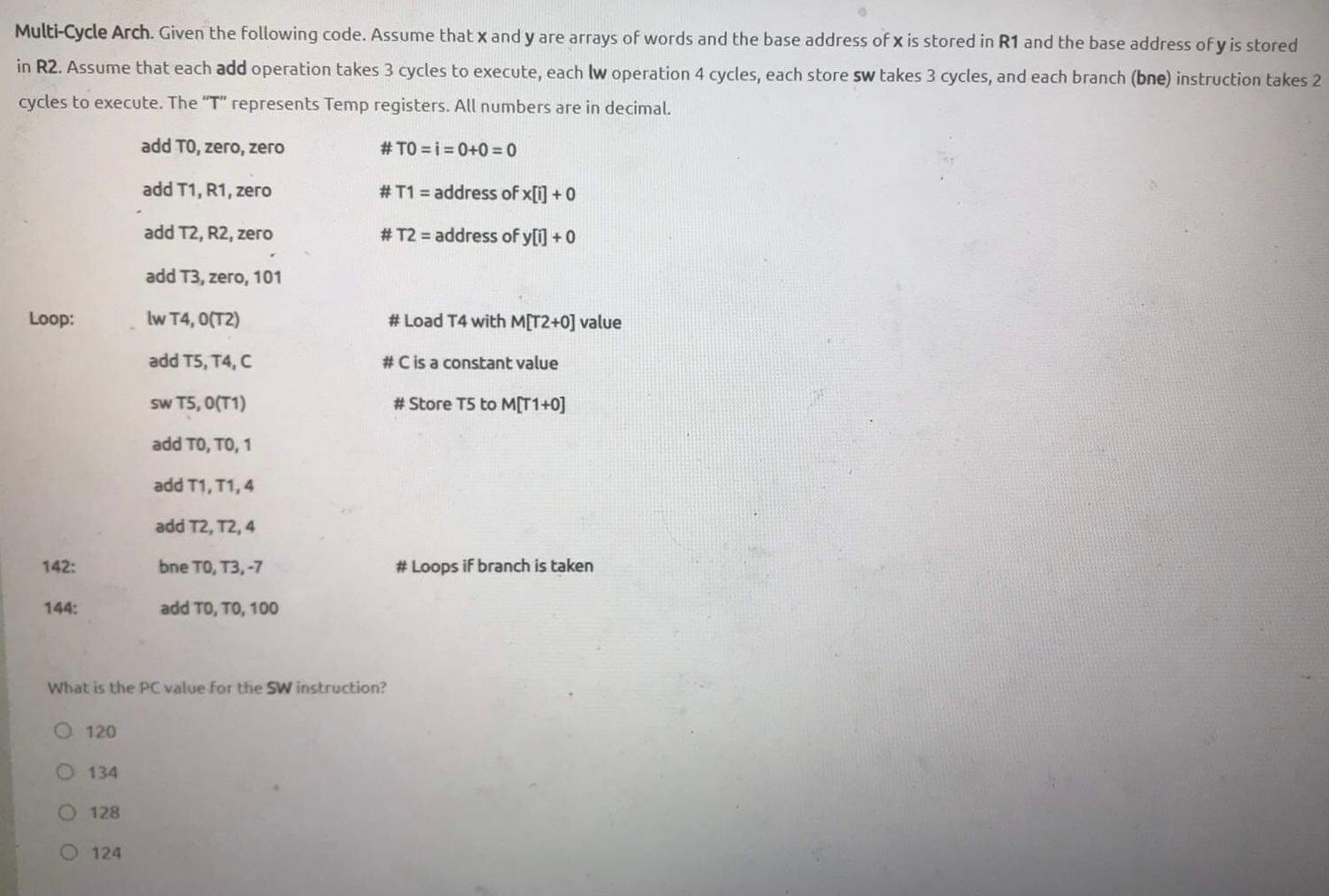

Multi-Cycle Arch. Given the following code. Assume that x and y are arrays of words and the base address of x is stored in R1 and the base address ofy is stored in R2. Assume that each add operation takes 3 cycles to execute, each lw operation 4 cycles, each store sw takes 3 cycles, and each branch (bne) instruction takes 2 cycles to execute. The "T" represents Temp registers. All numbers are in decimal. add TO, zero, zero # TO =i = 0+0 = 0 add T1, R1, zero #T1 = address of x[i] + 0 add T2, R2, zero # T2 = address of y[i] + 0 add T3, zero, 101 Loop: lw T4, 0(T2) #Load T4 with M[T2+0] value add T5, T4, # C is a constant value sw T5, O(T1) # Store T5 to M[T1+0] add TO, TO, 1 add T1, T1,4 add T2, T2,4 142: bne TO, T3, -7 # Loops if branch is taken 144: add TO, TO, 100 What is the PC value for the SW instruction? 120 134 128 124 Multi-Cycle Arch. Given the following code. Assume that x and y are arrays of words and the base address of x is stored in R1 and the base address ofy is stored in R2. Assume that each add operation takes 3 cycles to execute, each lw operation 4 cycles, each store sw takes 3 cycles, and each branch (bne) instruction takes 2 cycles to execute. The "T" represents Temp registers. All numbers are in decimal. add TO, zero, zero # TO =i = 0+0 = 0 add T1, R1, zero #T1 = address of x[i] + 0 add T2, R2, zero # T2 = address of y[i] + 0 add T3, zero, 101 Loop: lw T4, 0(T2) #Load T4 with M[T2+0] value add T5, T4, # C is a constant value sw T5, O(T1) # Store T5 to M[T1+0] add TO, TO, 1 add T1, T1,4 add T2, T2,4 142: bne TO, T3, -7 # Loops if branch is taken 144: add TO, TO, 100 What is the PC value for the SW instruction? 120 134 128 124

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts