Question: undefined Question 1 Consider an hypothetical memory access time: 1 memory bus clock cycle to send an address to the memory. 14 memory bus clock

undefined

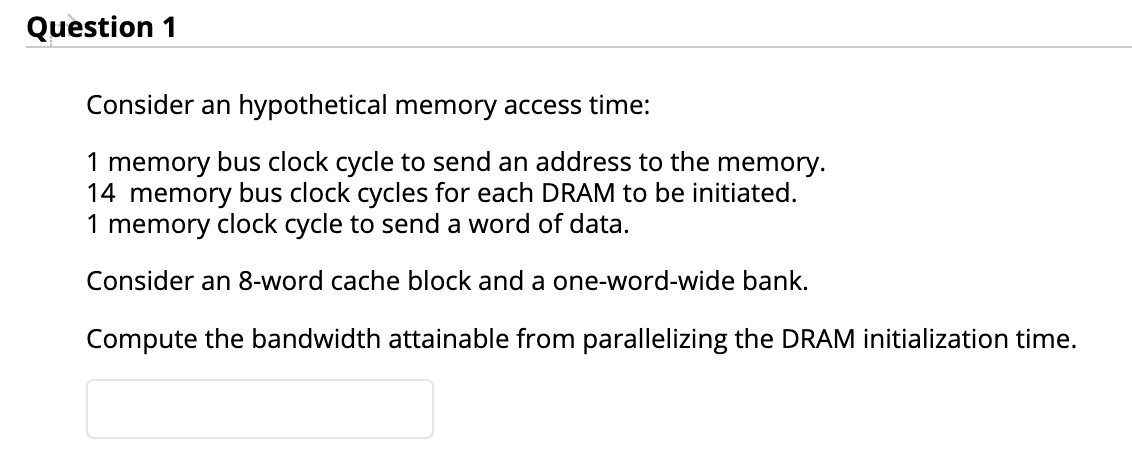

Question 1 Consider an hypothetical memory access time: 1 memory bus clock cycle to send an address to the memory. 14 memory bus clock cycles for each DRAM to be initiated. 1 memory clock cycle to send a word of data. Consider an 8-word cache block and a one-word-wide bank. Compute the bandwidth attainable from parallelizing the DRAM initialization time. Question 1 Consider an hypothetical memory access time: 1 memory bus clock cycle to send an address to the memory. 14 memory bus clock cycles for each DRAM to be initiated. 1 memory clock cycle to send a word of data. Consider an 8-word cache block and a one-word-wide bank. Compute the bandwidth attainable from parallelizing the DRAM initialization time

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts