Question: using vivado module Eeur Bit ALU (X, Y, Sin, Sa Cout); input (3:0) X, Y; input sin output (3:0)S; output Seutu assign Seutus)-XXtta endmedule Follow

using vivado

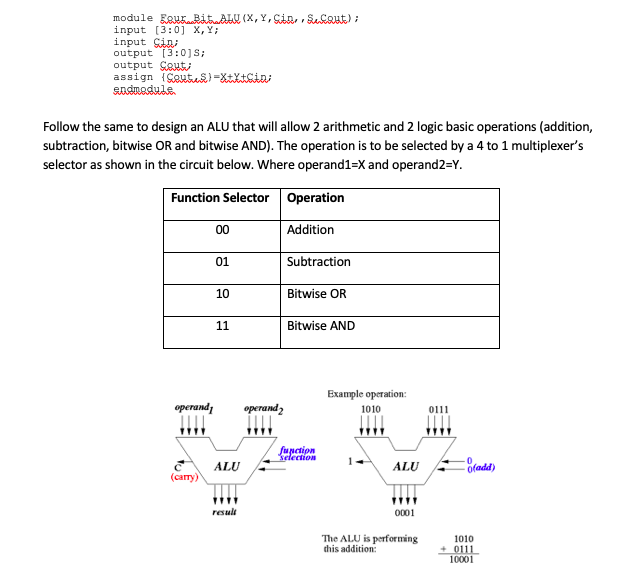

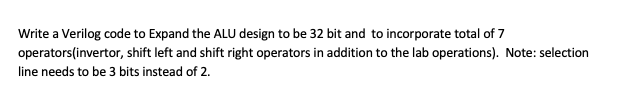

module Eeur Bit ALU (X, Y, Sin, Sa Cout); input (3:0) X, Y; input sin output (3:0)S; output Seutu assign Seutus)-XXtta endmedule Follow the same to design an ALU that will allow 2 arithmetic and 2 logic basic operations (addition, subtraction, bitwise OR and bitwise AND). The operation is to be selected by a 4 to 1 multiplexer's selector as shown in the circuit below. Where operand1=X and operand2=Y. Function Selector Operation 00 Addition 01 Subtraction 10 Bitwise OR 11 Bitwise AND operand operand2 Example operation: 1010 1111 0111 function selection ALU ALU Oraded) (carry) resul 0001 The ALU is performing this addition: 1010 + 0111 10001 Write a Verilog code to expand the ALU design to be 32 bit and to incorporate total of 7 operators(invertor, shift left and shift right operators in addition to the lab operations). Note: selection line needs to be 3 bits instead of 2. module Eeur Bit ALU (X, Y, Sin, Sa Cout); input (3:0) X, Y; input sin output (3:0)S; output Seutu assign Seutus)-XXtta endmedule Follow the same to design an ALU that will allow 2 arithmetic and 2 logic basic operations (addition, subtraction, bitwise OR and bitwise AND). The operation is to be selected by a 4 to 1 multiplexer's selector as shown in the circuit below. Where operand1=X and operand2=Y. Function Selector Operation 00 Addition 01 Subtraction 10 Bitwise OR 11 Bitwise AND operand operand2 Example operation: 1010 1111 0111 function selection ALU ALU Oraded) (carry) resul 0001 The ALU is performing this addition: 1010 + 0111 10001 Write a Verilog code to expand the ALU design to be 32 bit and to incorporate total of 7 operators(invertor, shift left and shift right operators in addition to the lab operations). Note: selection line needs to be 3 bits instead of 2

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts