Question: WRITE CODE IN SYSTEM VERILOG Instead of using a testbench waveform, as you have done in previous lab, you can write a Verilog test fixture

WRITE CODE IN SYSTEM VERILOG

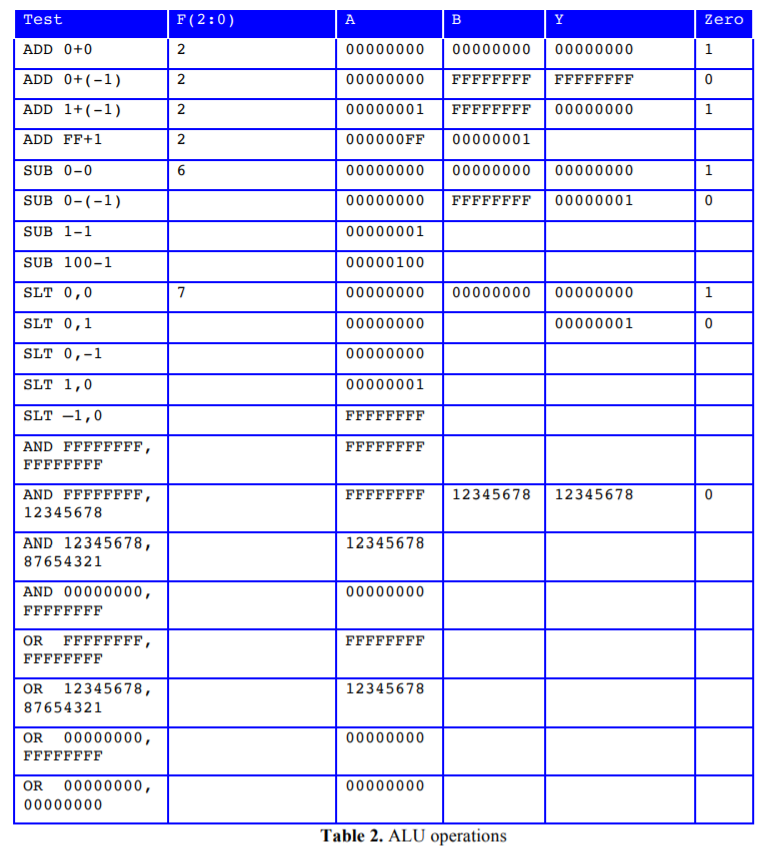

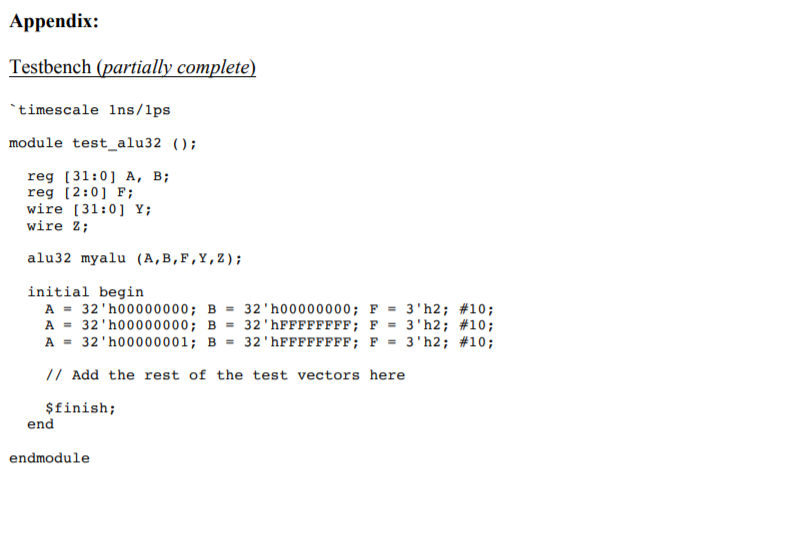

Instead of using a testbench waveform, as you have done in previous lab, you can write a Verilog test fixture (i.e. testbench) to test your 32-bit ALU. A template of testbench with the first 3 rows of Table 2 implementation is provided in Appendix. Test ADD 0+0 ADD 0+(-1) ADD 1+(-1) ADD FF+1 SUB 0-0 SUB 0-(-1) SUB 1-1 SUB 100-1 SLT 0,0 SLT 0,1 SLT 0,-1 SLT 1,0 SLT -1,0 AND FFFFFFFF F (2:0) 2 2 2 2 Zero 00000000 FFFFFFFF FFFFFFFF 00000001 FFFFFFFF 00000000 00000OFF 00000001 00000000 FFFFFFFF 00000001 00000001 00000100 00000001 00000001 AND FFFFFFFF 12345678 FFFFFFFF 12345678 12345678 AND 12345678, 87654321 12345678 AND 00000000, 12345678 OR 12345678, 87654321 OR 00000000, OR 00000000, Table 2. ALU operations Appendix: Testbench (partially complete) timescale lns/lps module test alu32 reg (31:0] A, B; reg [2:0] F: wire [31:0] Y; wire Z; alu32 myalu (A,B,F,Y,2); initial begin A- 32 'h00000000; B- 32,h00000000; F- 3'h2 ; #10; A- 32 'h00000000; B- 32'hFFFFFFFF; F- 3.h2 ; #10; A- 32 'h00000001; B- 32, hFFFFFFFF; F- 3'h2 ; #10; // Add the rest of the test vectors here Sfinish; end endmodule Instead of using a testbench waveform, as you have done in previous lab, you can write a Verilog test fixture (i.e. testbench) to test your 32-bit ALU. A template of testbench with the first 3 rows of Table 2 implementation is provided in Appendix. Test ADD 0+0 ADD 0+(-1) ADD 1+(-1) ADD FF+1 SUB 0-0 SUB 0-(-1) SUB 1-1 SUB 100-1 SLT 0,0 SLT 0,1 SLT 0,-1 SLT 1,0 SLT -1,0 AND FFFFFFFF F (2:0) 2 2 2 2 Zero 00000000 FFFFFFFF FFFFFFFF 00000001 FFFFFFFF 00000000 00000OFF 00000001 00000000 FFFFFFFF 00000001 00000001 00000100 00000001 00000001 AND FFFFFFFF 12345678 FFFFFFFF 12345678 12345678 AND 12345678, 87654321 12345678 AND 00000000, 12345678 OR 12345678, 87654321 OR 00000000, OR 00000000, Table 2. ALU operations Appendix: Testbench (partially complete) timescale lns/lps module test alu32 reg (31:0] A, B; reg [2:0] F: wire [31:0] Y; wire Z; alu32 myalu (A,B,F,Y,2); initial begin A- 32 'h00000000; B- 32,h00000000; F- 3'h2 ; #10; A- 32 'h00000000; B- 32'hFFFFFFFF; F- 3.h2 ; #10; A- 32 'h00000001; B- 32, hFFFFFFFF; F- 3'h2 ; #10; // Add the rest of the test vectors here Sfinish; end endmodule

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts