Question: Assume both benchmarks have a base CPI of 1 (ideal L2 cache). If having non-blocking cache improves the average number of concurrent L2 misses from

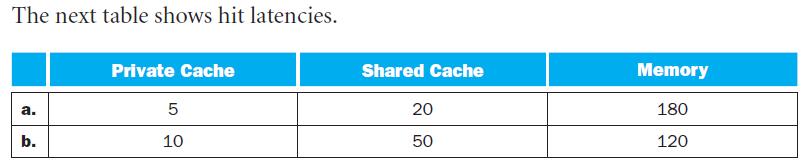

Assume both benchmarks have a base CPI of 1 (ideal L2 cache). If having non-blocking cache improves the average number of concurrent L2 misses from 1 to 2, how much performance improvement does this provide over a shared L2 cache? How much improvement can be achieved over private L2?

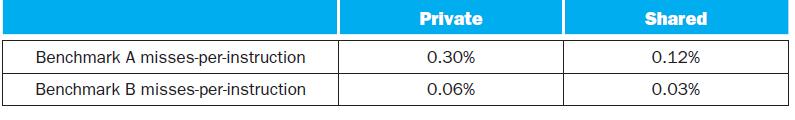

Both Barcelona and Nehalem are chip multiprocessors (CMPs), having multiple cores and their caches on a single chip. CMP on-chip L2 cache design has interesting trade-offs. The following table shows the miss rates and hit latencies for two benchmarks with private vs. shared L2 cache designs. Assume L1 cache misses once every 32 instructions.

Benchmark A misses-per-instruction Benchmark B misses-per-instruction Private 0.30% 0.06% Shared 0.12% 0.03%

Step by Step Solution

3.37 Rating (150 Votes )

There are 3 Steps involved in it

Benchmark A CPI with Shared L2 1 0384 20 868 CPI with NonBlocking L2 1 0384 2 20 1536 Performance Im... View full answer

Get step-by-step solutions from verified subject matter experts