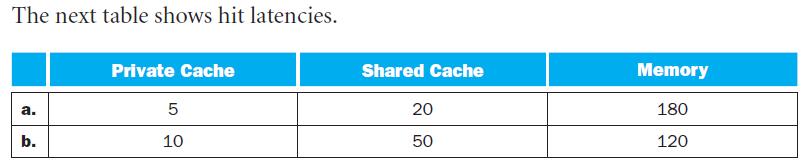

Question: Shared cache latency increases with the CMP size. Choose the best design if the shared cache latency doubles. Off-chip bandwidth becomes the bottleneck as the

Shared cache latency increases with the CMP size. Choose the best design if the shared cache latency doubles. Off-chip bandwidth becomes the bottleneck as the number of CMP cores increases. Choose the best design if offchip memory latency doubles.

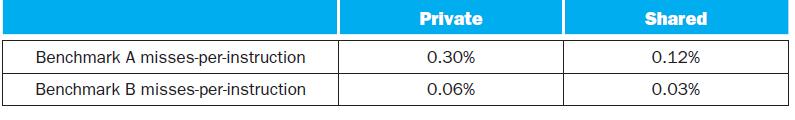

Both Barcelona and Nehalem are chip multiprocessors (CMPs), having multiple cores and their caches on a single chip. CMP on-chip L2 cache design has interesting trade-offs. The following table shows the miss rates and hit latencies for two benchmarks with private vs. shared L2 cache designs. Assume L1 cache misses once every 32 instructions.

Benchmark A misses-per-instruction Benchmark B misses-per-instruction Private 0.30% 0.06% Shared 0.12% 0.03%

Step by Step Solution

3.52 Rating (152 Votes )

There are 3 Steps involved in it

To address the scenarios where shared cache latency doubles and offchip memory latency doubles lets ... View full answer

Get step-by-step solutions from verified subject matter experts