Question: This exercise explores how exception handling affects control unit design and processor clock cycle time. The first three problems in this exercise refer to the

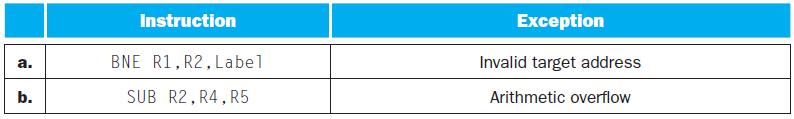

This exercise explores how exception handling affects control unit design and processor clock cycle time. The first three problems in this exercise refer to the following MIPS instruction that triggers an exception:

Some of the control signals generated in the ID stage are stored into the ID/EX pipeline register, and some go directly into the EX stage. Explain why, using this instruction as an example.

a. b. Instruction BNE R1, R2, Label SUB R2, R4, R5 Exception Invalid target address Arithmetic overflow

Step by Step Solution

3.39 Rating (168 Votes )

There are 3 Steps involved in it

The instruction BNE R1 R2 Label uses the following control signals in the ID stage RegWrite Indicates whether the register destination operand is writ... View full answer

Get step-by-step solutions from verified subject matter experts