Question: We can make the EX stage faster if we check for exceptions in the stage after the one in which the exceptional condition occurs. Using

We can make the EX stage faster if we check for exceptions in the stage after the one in which the exceptional condition occurs. Using this instruction as an example, describe the main disadvantage of this approach.

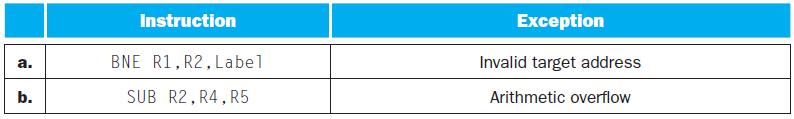

This exercise explores how exception handling affects control unit design and processor clock cycle time. The first three problems in this exercise refer to the following MIPS instruction that triggers an exception:

a. b. Instruction BNE R1, R2, Label SUB R2, R4, R5 Exception Invalid target address Arithmetic overflow

Step by Step Solution

3.32 Rating (167 Votes )

There are 3 Steps involved in it

If we choose to check for exceptions in the stage after the one in which the exceptional condition occurs it can lead to a disadvantage known as delay... View full answer

Get step-by-step solutions from verified subject matter experts