Question: 1. Write the Verilog code for a full adder, using logic equations (Data-Flow Model). Assume that the full adder has a 5-ns delay 2. Write

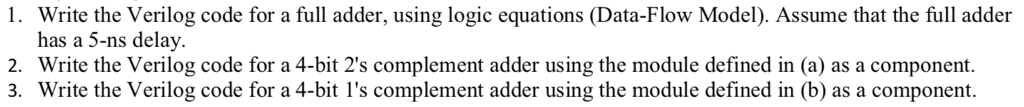

1. Write the Verilog code for a full adder, using logic equations (Data-Flow Model). Assume that the full adder has a 5-ns delay 2. Write the Verilog code for a 4-bit 2's complement adder using the module defined in (a) as a component. 3. Write the Verilog code for a 4-bit 1's complement adder using the module defined in (b) as a component. 1. Write the Verilog code for a full adder, using logic equations (Data-Flow Model). Assume that the full adder has a 5-ns delay 2. Write the Verilog code for a 4-bit 2's complement adder using the module defined in (a) as a component. 3. Write the Verilog code for a 4-bit 1's complement adder using the module defined in (b) as a component

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts