Question: The MIPS single cycle CPU design discussed in class (and shown in Problem No. 1) does not include support for the jr instruction. What

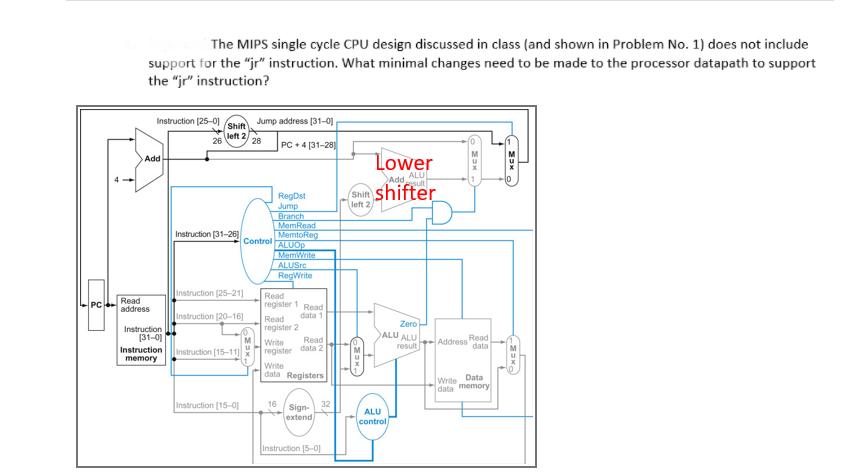

The MIPS single cycle CPU design discussed in class (and shown in Problem No. 1) does not include support for the "jr" instruction. What minimal changes need to be made to the processor datapath to support the "jr" instruction? Instruction (25-0) Jump address (31-01 Shift left 2 28 PC + 4 [31-28 Lower Add ALU Shin shifter Add Hsult RegDst Jump Branch MemRead MemtoReg ALUOP MemWnite ALUSrc RegWrite left 2, Instruction (31-26 Control Instruction (25-21] Read Read address register 1 Read Instruction [20-16] data 1 Read register 2 Zero Instruction ALU ALU Addness Read result [31-0] Read Write data Instruction memory Instruction (15-11 register data 2 Write data Registers Write Data data memory Instruction [15-0 16 Sign- 32 ALU extend control Instruction [5-0]

Step by Step Solution

3.52 Rating (162 Votes )

There are 3 Steps involved in it

To begin you will be creating a behavioral model of the singlecycle MIPS CPU in Verilog One possible incomplete implementation of the MIPS CPU is shown below in block diagram form There are a few key ... View full answer

Get step-by-step solutions from verified subject matter experts