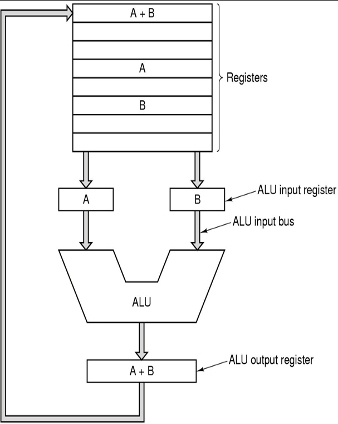

Question: Consider the data path of a CPU on the right. With this configuration a register - to - register operation ( e . g .

Consider the data path of a CPU on the right. With this configuration a registertoregister operation eg CAB takes clock cycles; ie a fixed amount of time regardless of the complexity of the ALU operation. In the first cycle data is loaded into the ALU input registers from the main registers. For all registers the loading operation takes a maximum of ns nanoseconds In the second cycle the ALU operation is started and completed. The ALU can compute types of operations that take

nsec each. At the end of the ALU operation the data will be ready in the ALU output register. Note that in this architecture every ALU operation needs to be completed in a single clock cycle. In the third cycle the output is written back to the main registers. This also takes a maximum of nsec

a Find the maximum clock frequency and bandwidth in MIPS that this microprocessor can handle for repetitive registertoregister operations if the register load, store and ALU operations are performed sequentially for each instruction ie without any overlap between

instructions. Note that the clock frequency will remain constant once set for operation and the cycle time will be the same for all clock cycles.

b Repeat part a if the data path operates in a pipelined fashion, ie all units are kept busy through parallel operation. In any given cycle, as the input registers are being loaded, the ALU is performing an operation for the previous instruction and the data from the previous ALU operation.

is being written back to the destination registers. Assume there are no register readwrite conflicts.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock