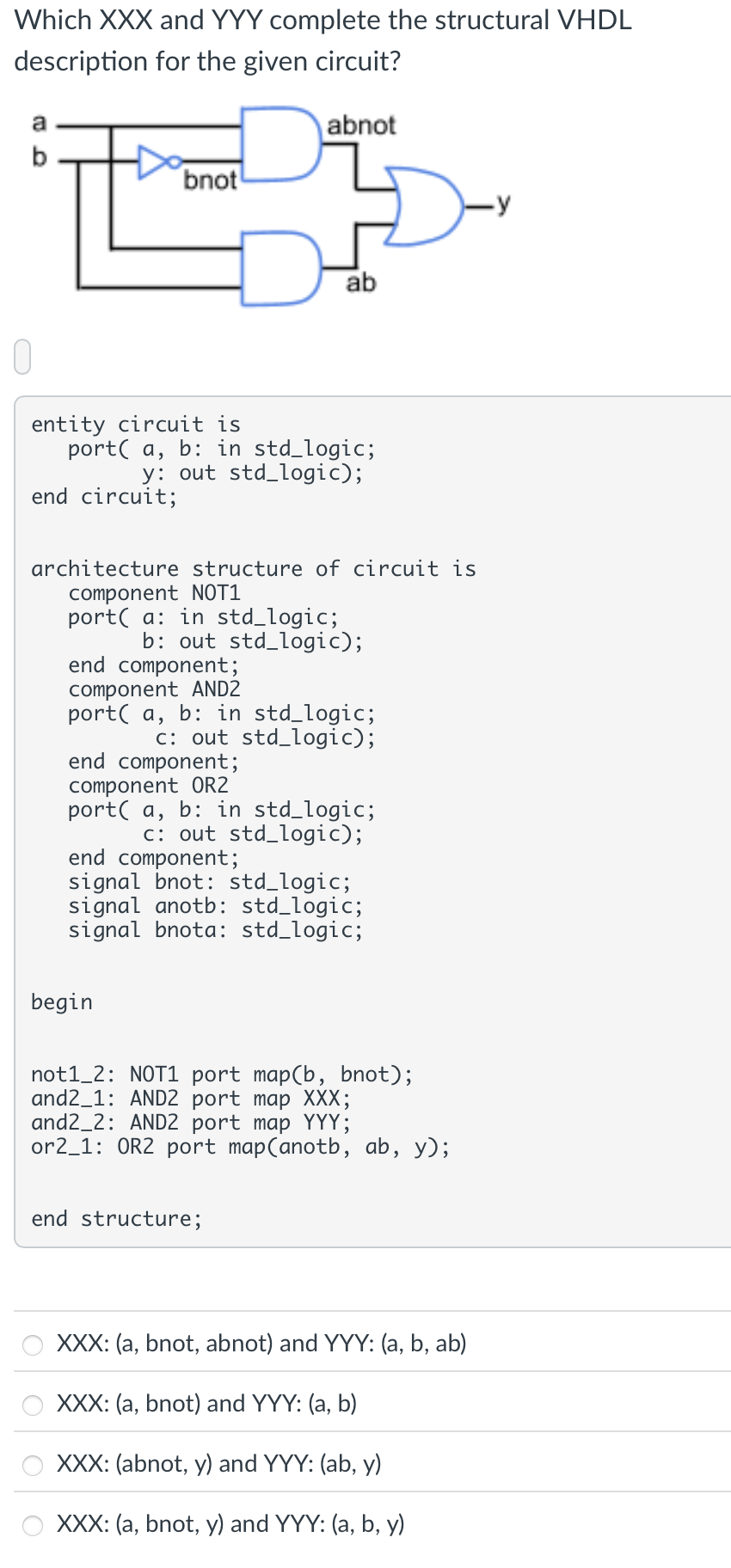

Question: ` ` ` entity circuit is port ( a , b: in std _ logic; y: out std _ logic ) ; end circuit; architecture

entity circuit is

port a b: in stdlogic;

y: out stdlogic;

end circuit;

architecture structure of circuit is

component NOT

port a: in stdlogic;

b: out stdlogic;

end component;

component AND

port a b: in stdlogic;

c: out stdlogic;

end component;

component OR

port a b: in stdlogic;

c: out stdlogic;

end component;

signal bnot: stdlogic;

signal anotb: stdlogic;

signal bnota: stdlogic;

begin

not: NOT port mapb bnot;

and: AND port map XXX;

and: AND port map YYY;

or: OR port mapanotb ab y;

end structure;

X X X : a bnot, abnot and YYY: a b ab

X X X:a b n o t and Y Y Y:a b

X X X : abnot y and YYY: ab y

X X X:a bnot, y and mathrmYYY:mathrmamathrmbmathrmy

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock