Question: Performance ( 6 p t ) . When processor designers consider possible improvement to the processor datapath, the decision usually depends on the cost /

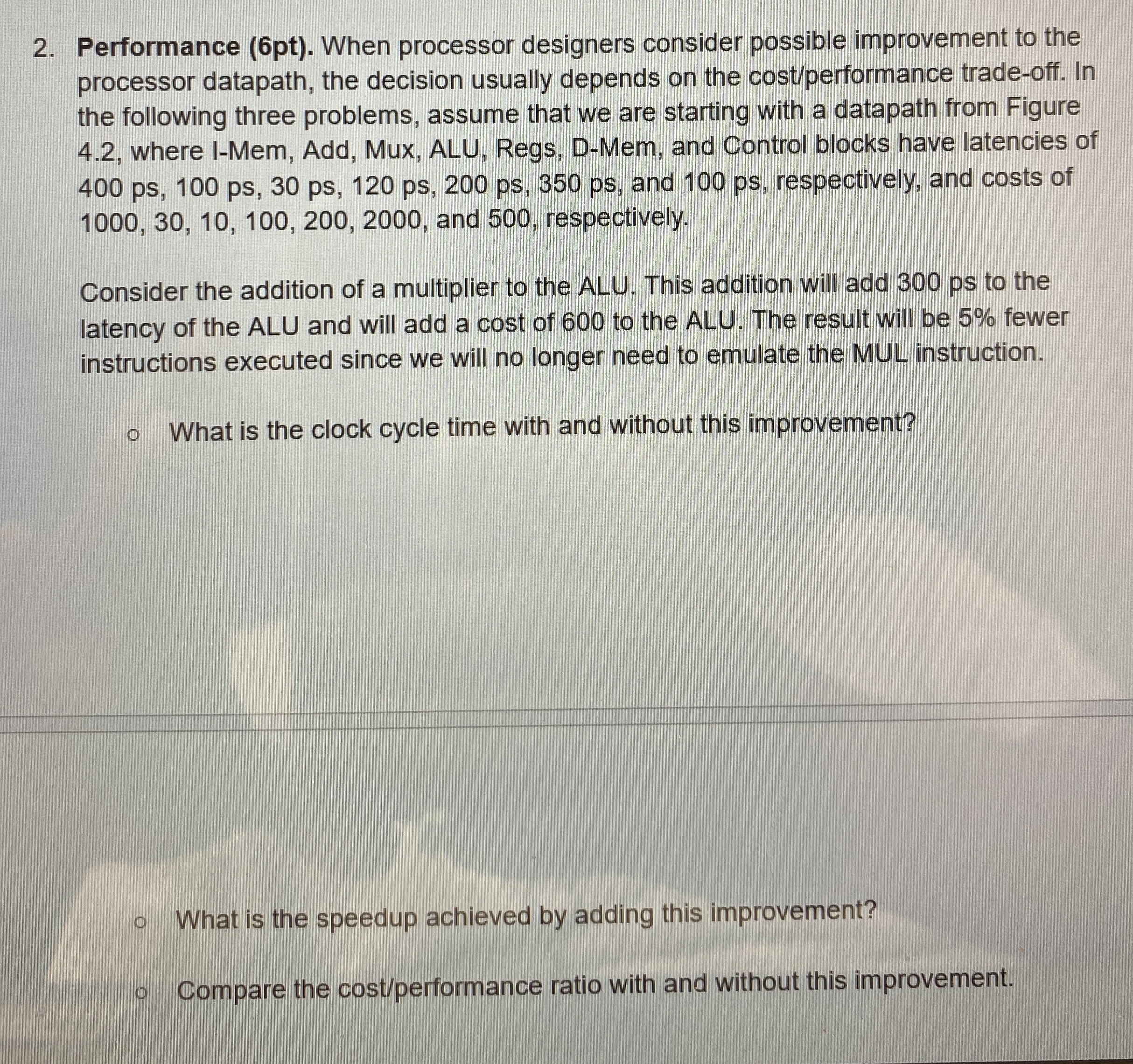

Performance When processor designers consider possible improvement to the processor datapath, the decision usually depends on the costperformance tradeoff. In the following three problems, assume that we are starting with a datapath from Figure where IMem, Add, Mux, ALU, Regs, DMem, and Control blocks have latencies of and ps respectively, and costs of and respectively.

Consider the addition of a multiplier to the ALU. This addition will add ps to the latency of the ALU and will add a cost of to the ALU. The result will be fewer instructions executed since we will no longer need to emulate the MUL instruction.

What is the clock cycle time with and without this improvement?

What is the speedup achieved by adding this improvement?

Compare the costperformance ratio with and without this improvement.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock