Question: Question 2. Assume that logic blocks needed to implement a processor's datapath have the following latencies. Ignore the Program Counter adder, i.e., PC+4. Add Mux

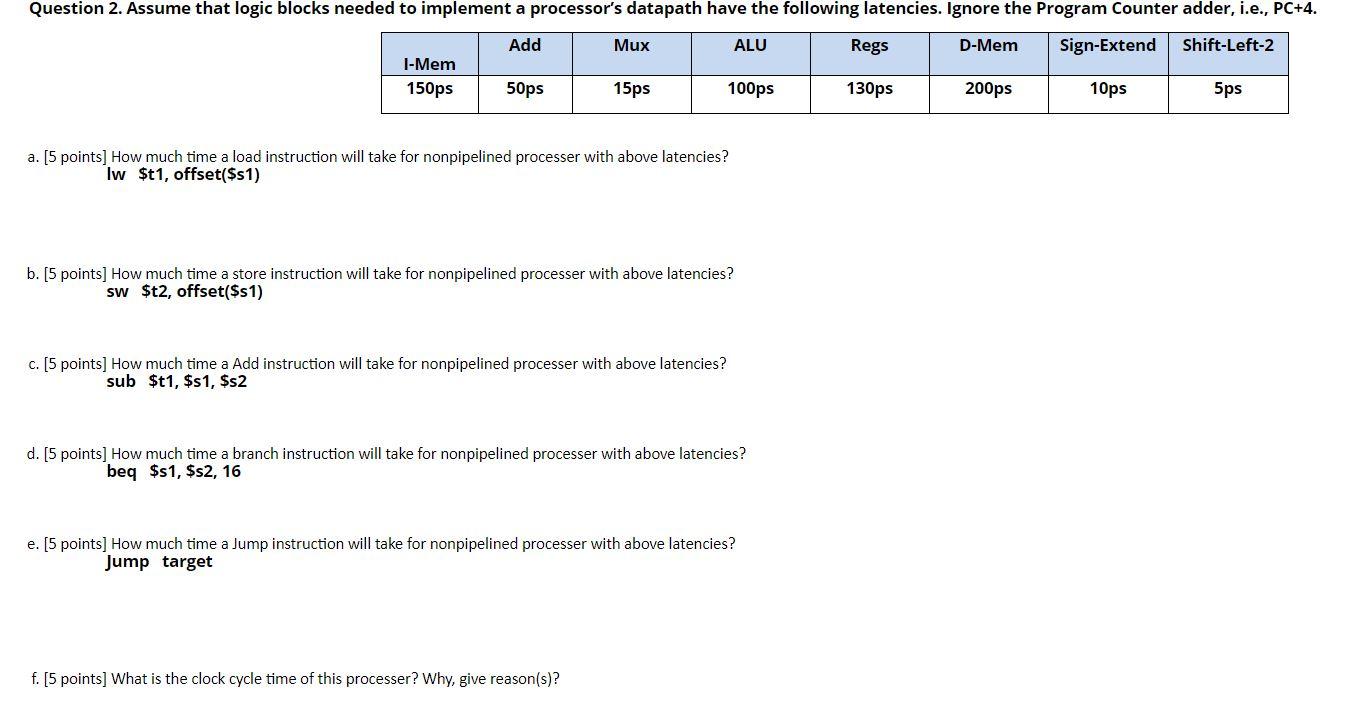

Question 2. Assume that logic blocks needed to implement a processor's datapath have the following latencies. Ignore the Program Counter adder, i.e., PC+4. Add Mux ALU Regs D-Mem Sign-Extend Shift-Left-2 I-Mem 150ps 50ps 15ps 100ps 130ps 200ps 10ps 5ps a. [5 points) How much time a load instruction will take for nonpipelined processer with above latencies? lw $t1, offset($s1) b. [5 points] How much time a store instruction will take for nonpipelined processer with above latencies? sw $t2, offset($s 1) c. [5 points) How much time a Add instruction will take for nonpipelined processer with above latencies? sub $t1,$s 1, $s2 d. [5 points] How much time a branch instruction will take for nonpipelined processer with above latencies? beq $81, $s2, 16 e. [5 points) How much time a Jump instruction will take for nonpipelined processer with above latencies? Jump target f. [5 points] What is the clock cycle time of this processer? Why, give reason(s)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts