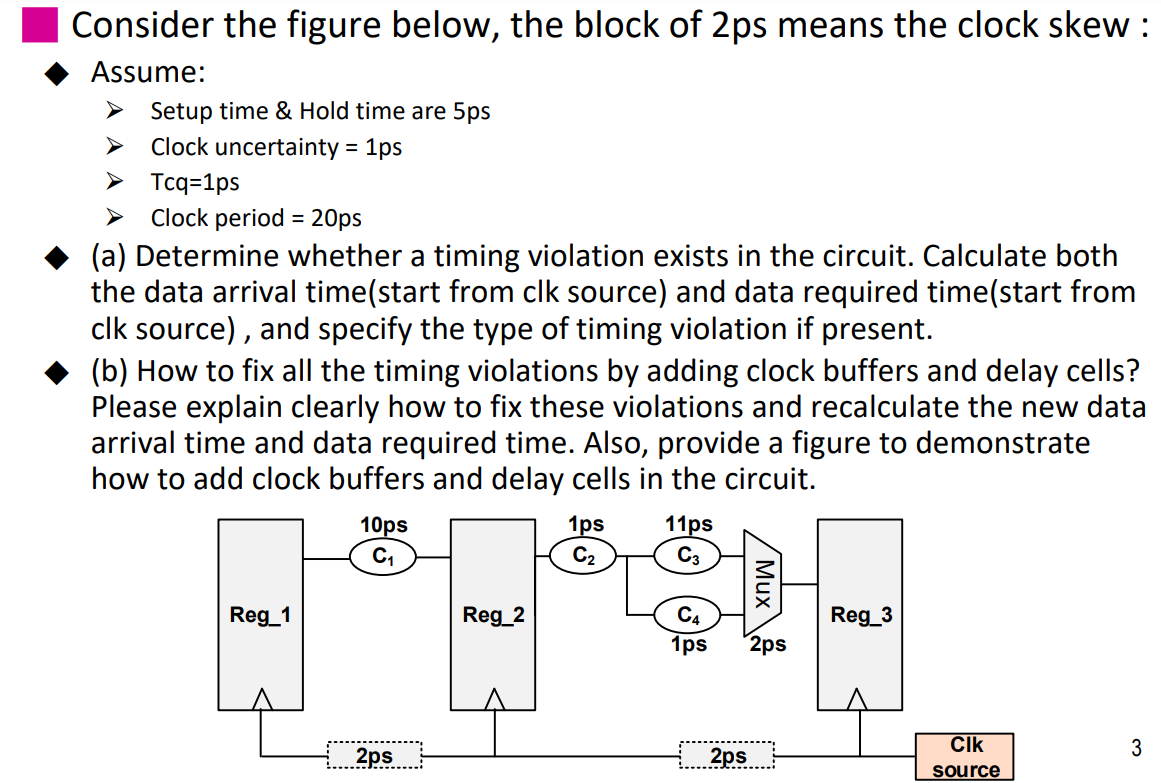

Question: ( square ) Consider the figure below, the block of 2 ps means the clock skew : - Assume: > Setup time

square Consider the figure below, the block of ps means the clock skew :

Assume:

Setup time & Hold time are ps

Clock uncertainty ps

mathrmTcqmathrmps

Clock period ps

a Determine whether a timing violation exists in the circuit. Calculate both the data arrival timestart from clk source and data required timestart from clk source and specify the type of timing violation if present.

b How to fix all the timing violations by adding clock buffers and delay cells? Please explain clearly how to fix these violations and recalculate the new data arrival time and data required time. Also, provide a figure to demonstrate how to add clock buffers and delay cells in the circuit.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock