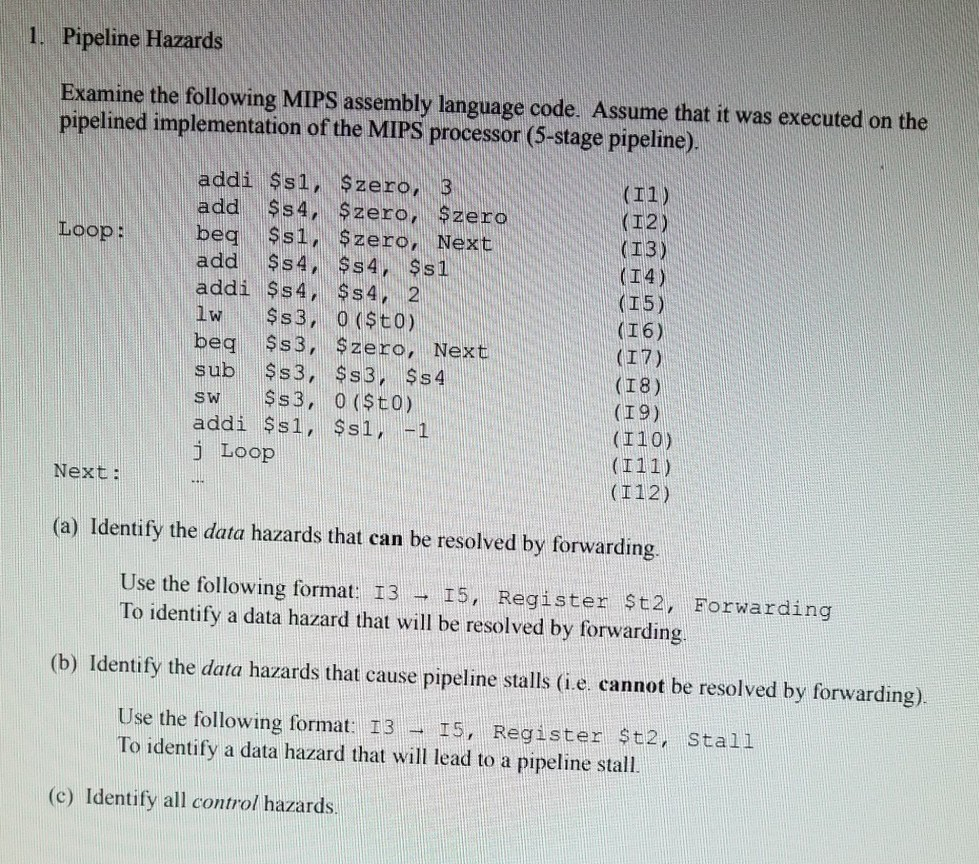

Question: 1. Pipeline Hazards Examine the following MIPS assembly language code. Assume that it was executed on the pipelined implementation of the MIPS processor (5-stage pipeline)

1. Pipeline Hazards Examine the following MIPS assembly language code. Assume that it was executed on the pipelined implementation of the MIPS processor (5-stage pipeline) addi $s1, Szero, 3 add $s4, Szero, Szero beg Ssl, Szeror Next add $s4, $s4, $si addi $s4, $54, 2 (I2) (I3) I 4 (I5) (I6) (I7) (I8) (I9) (I10) beg $s3, Szero, Next sub $s3, Ssi3, $s4 addi $s1r Ssl, j Loop Next: (I12) (a) Identify the data hazards that can be resolved by forwarding. Use the following format: 13 15, Register $t2, Forwarding To identify a data hazard that will be resolved by forwarding (b) Identify the data hazards that cause pipeline stalls (i e cannot be resolved by forwarding) Use the following format 13 - I5, Register $t2, Stall To identify a data hazard that will lead to a pipeline stall. (c) Identify all control hazards

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts