Question: 3. Write a verilog code and testbench code and test your design with different input combinations. 1. You are supposed to design an LFSR according

3. Write a verilog code and testbench code and test your design with different input combinations.

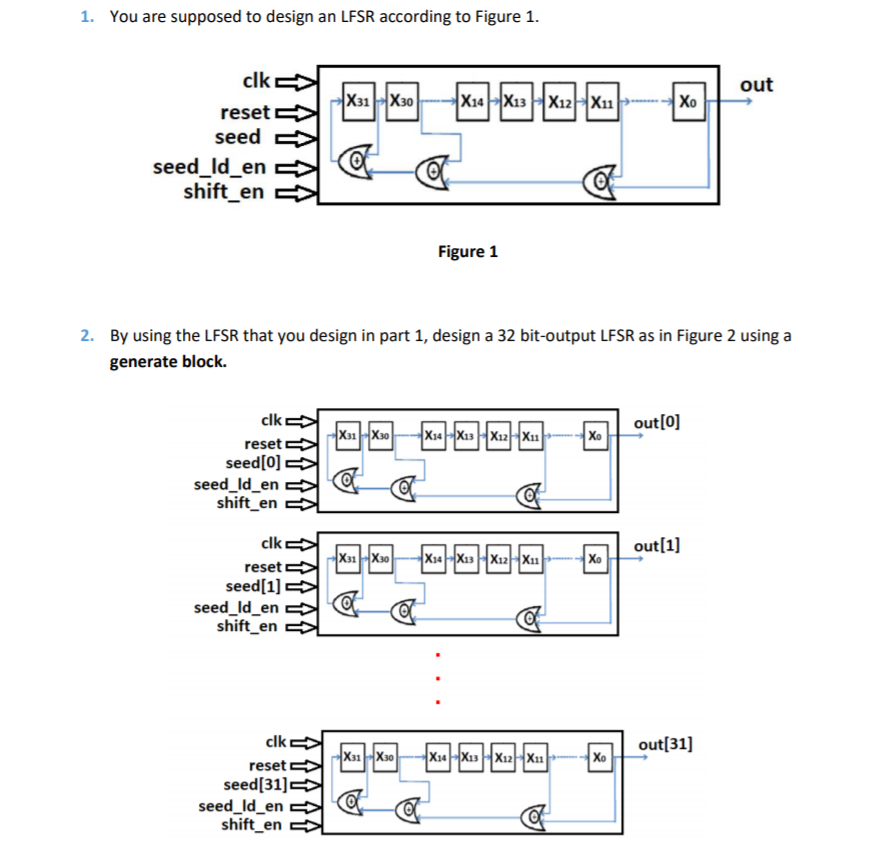

1. You are supposed to design an LFSR according to Figure 1. out X31X30 X14X13 HX12X11 clk 2 reset seed seed_ld_en shift_en Figure 1 2. By using the LFSR that you design in part 1, design a 32 bit-output LFSR as in Figure 2 using a generate block. out[0] -X1/X30 X14X13 HX12 Xu clk reset seed[0] => seed_Id_en shift_en @ out[1] |X31X30 X14X13 HX12 Xu | Xo clk reset seed[1] = seed_ld_en shift_en clk out[31] X31X30 X14 H-X13 HX12 HX11 Xo reset seed[31] seed_ld_en shift_en

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts