![]()

![]() New Semester Started

Get 50% OFF

Study Help!

--h --m --s

Claim Now

New Semester Started

Get 50% OFF

Study Help!

--h --m --s

Claim Now

![]()

![]()

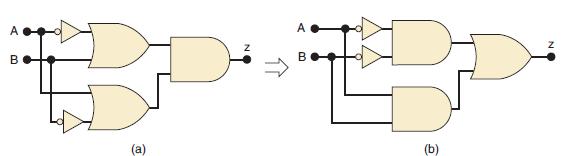

![SUBDESIGN Figure 4-63 ( ) P, q, r S VARIABLE status [2..0] BEGIN END CASE; : INPUT; :OUTPUT; END; :NODE;](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1699/6/8/7/564654f2c8c0ec641699687563891.jpg)

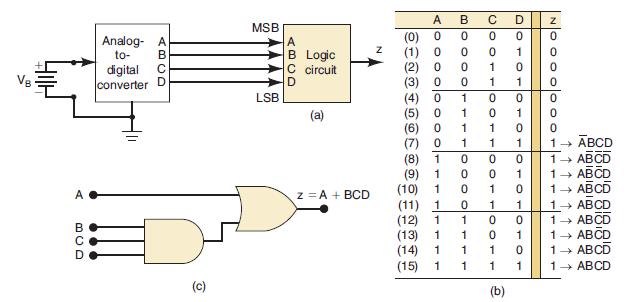

![SUBDESIGN Figure 4-57 digital_value [3..0] ( Z BEGIN IF digital value [] > 6 THEN z = VCC; ELSE z = GND; END](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1699/6/8/7/041654f2a8109be01699687041803.jpg)

![SUBDESIGN Figure 4-57 digital_value [3..0] ( Z ) BEGIN IF digital_value [] > 6 THEN z = VCC; ELSE z = GND;](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1699/6/9/2/481654f3fc127b2b1699692481835.jpg)