![]()

![]() New Semester Started

Get 50% OFF

Study Help!

--h --m --s

Claim Now

New Semester Started

Get 50% OFF

Study Help!

--h --m --s

Claim Now

![]()

![]()

![P From D D transmitter Even-parity checker (b) Error (E) (1 = error 0= no error]](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1699/6/2/5/244654e391c6b1681699625247537.jpg)

![(MSB) A/D converter (LSB) Input port P1[7] P1 [6] P1[5] P1[4] P1[3] P1 [2] P1[1] P1[0] P1](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1699/6/2/5/870654e3b8ee63a81699625874756.jpg)

![Insert Coin Quarter Dime Nickel Logic Circuit D cents[4.00] N Five-bit array representing coin value](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1699/6/2/6/103654e3c77f15e11699626107828.jpg)

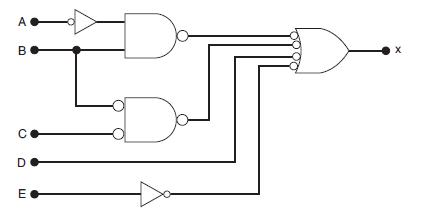

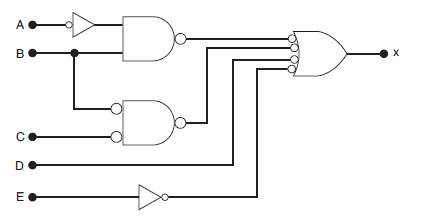

![A B O D E A+B (A + B)C (b) (A + B)C D + (A + B)C x = [D+ (A + B)C] E](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1699/5/9/8/479654dd08fbb7bb1699598482402.jpg)