![]()

![]() New Semester Started

Get 50% OFF

Study Help!

--h --m --s

Claim Now

New Semester Started

Get 50% OFF

Study Help!

--h --m --s

Claim Now

![]()

![]()

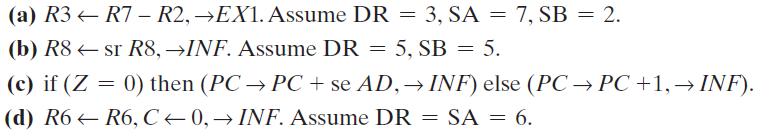

![Instruction Register Transfer R[0] R[7] R[3] R[1] M[R[4]] R[2] R[5]+2 R[3] sl R[6] if (R([4] = 0) PC](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1704/5/6/8/2286599a5a42333e1704568225237.jpg)

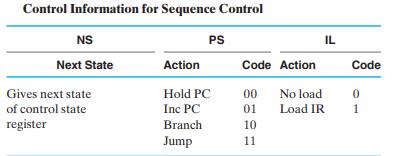

![Control-Word Information for Datapath DX AX BX Code MB Code FS R[DR] R[SA] R[SB] OXXX Register 0 F = A R8 R8](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1704/5/6/8/5726599a6fc9e2ec1704568570419.jpg)

![R[DR] R[SB] + M[R[SA]]](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1704/5/6/8/6946599a776cd8591704568693070.jpg)