![]()

![]() New Semester Started

Get 50% OFF

Study Help!

--h --m --s

Claim Now

New Semester Started

Get 50% OFF

Study Help!

--h --m --s

Claim Now

![]()

![]()

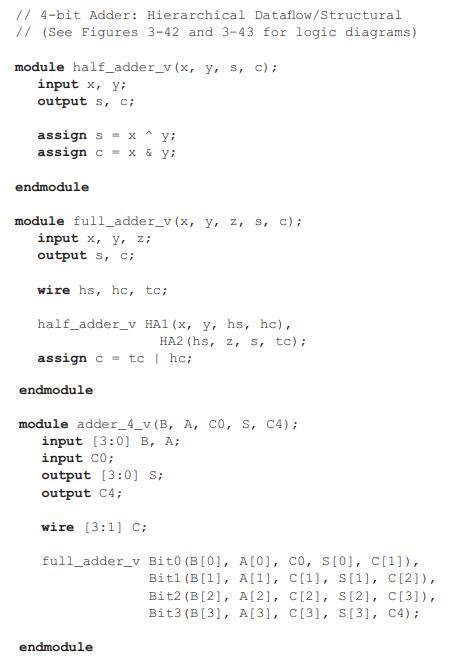

![// 4-bit Adder: Behavioral Verilog Description module adder_4_b_v (A, B, CO, S, C4); input [3:0] A, B; input](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1704/4/5/9/0846597fb4ce3c741704459084682.jpg)

![//4-bit Adder: Behavioral Verilog Description module adder_4_b_v (A, B, CO, S, C4); input [3:0] A, B; input](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1704/4/5/8/9836597fae7647951704458983141.jpg)

![0/0 or 1/1 0/1 B2=0] 0/0 or 1/1 B3 = X B3=0 0/1 (B1=0) 0/1 1/0 0/1 Init B2 = 1 (d) 1/0 1/0 B1 = 1 0/1 or 1/1](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1704/4/6/6/390659817d649d421704466389860.jpg)