![]()

![]() New Semester Started

Get 50% OFF

Study Help!

--h --m --s

Claim Now

New Semester Started

Get 50% OFF

Study Help!

--h --m --s

Claim Now

![]()

![]()

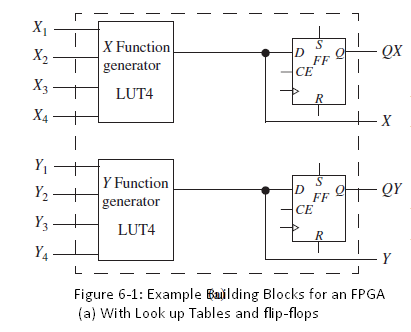

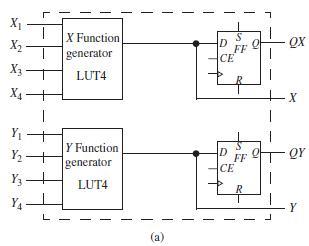

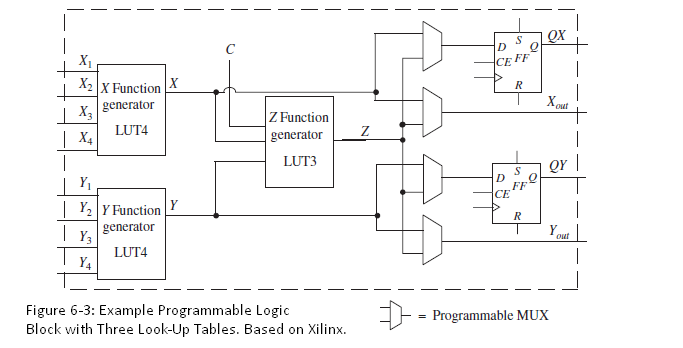

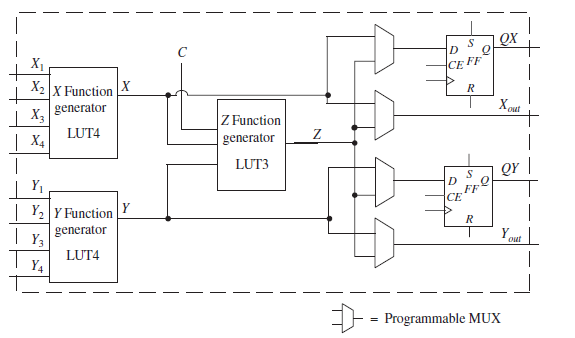

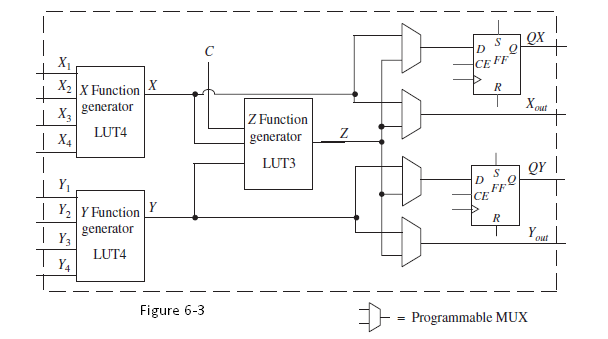

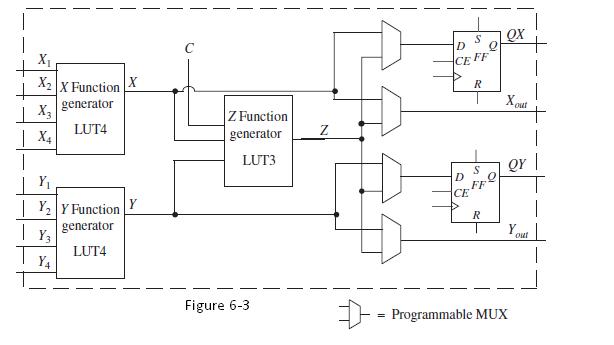

![| X] XX Function | X,]X Function X, generator OX FF X generator FF O CE QX CE So LUT4 M1 х, LUT4 X4 Y1 YlY Function Y g](https://dsd5zvtm8ll6.cloudfront.net/si.question.images/images/question_images/1547/1/1/7/3545c37232a38d6e1547099978277.jpg)

![always @ (posedge CLK) begin if (CLR) else if (Ld) else if (LS) end Ld Q <= 4'b0000; Q <= D; Q <= {Q[2:0], Rin}; LS Left](https://dsd5zvtm8ll6.cloudfront.net/si.question.images/images/question_images/1546/8/6/4/2725c3346904862f1546846892418.jpg)